ডিআইপি বুঝুন

ডিআইপি হলো একটি প্লাগ-ইন। এইভাবে প্যাকেজ করা চিপগুলিতে দুটি সারি পিন থাকে, যা সরাসরি ডিআইপি কাঠামো সহ চিপ সকেটে ঢালাই করা যেতে পারে অথবা একই সংখ্যক গর্ত সহ ঢালাই অবস্থানে ঢালাই করা যেতে পারে। পিসিবি বোর্ড ছিদ্র ঢালাই করা খুবই সুবিধাজনক, এবং মাদারবোর্ডের সাথে এর সামঞ্জস্য ভালো, তবে এর প্যাকেজিং এলাকা এবং বেধ তুলনামূলকভাবে বড় হওয়ায় এবং সন্নিবেশ এবং অপসারণের প্রক্রিয়ায় পিনটি সহজেই ক্ষতিগ্রস্ত হয়, নির্ভরযোগ্যতা কম থাকে।

DIP হল সবচেয়ে জনপ্রিয় প্লাগ-ইন প্যাকেজ, অ্যাপ্লিকেশন পরিসরে স্ট্যান্ডার্ড লজিক আইসি, মেমোরি LSI, মাইক্রোকম্পিউটার সার্কিট ইত্যাদি অন্তর্ভুক্ত রয়েছে। ছোট প্রোফাইল প্যাকেজ (SOP), যা SOJ (J-টাইপ পিন ছোট প্রোফাইল প্যাকেজ), TSOP (পাতলা ছোট প্রোফাইল প্যাকেজ), VSOP (খুব ছোট প্রোফাইল প্যাকেজ), SSOP (হ্রাসকৃত SOP), TSSOP (পাতলা হ্রাসকৃত SOP) এবং SOT (ছোট প্রোফাইল ট্রানজিস্টর), SOIC (ছোট প্রোফাইল ইন্টিগ্রেটেড সার্কিট) ইত্যাদি থেকে প্রাপ্ত।

ডিআইপি ডিভাইস অ্যাসেম্বলি ডিজাইনের ত্রুটি

পিসিবি প্যাকেজের গর্তটি ডিভাইসের চেয়ে বড়।

পিসিবি প্লাগ-ইন গর্ত এবং প্যাকেজ পিনের গর্তগুলি স্পেসিফিকেশন অনুসারে আঁকা হয়। প্লেট তৈরির সময় গর্তগুলিতে তামার প্রলেপের প্রয়োজনের কারণে, সাধারণ সহনশীলতা প্লাস বা মাইনাস 0.075 মিমি। যদি পিসিবি প্যাকেজিং গর্তটি ভৌত ডিভাইসের পিনের চেয়ে খুব বড় হয়, তবে এটি ডিভাইসটি আলগা হয়ে যাবে, অপর্যাপ্ত টিন, এয়ার ওয়েল্ডিং এবং অন্যান্য মানের সমস্যার সৃষ্টি করবে।

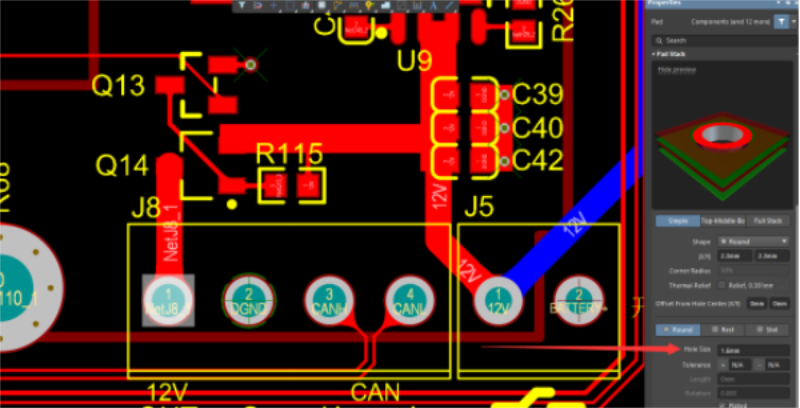

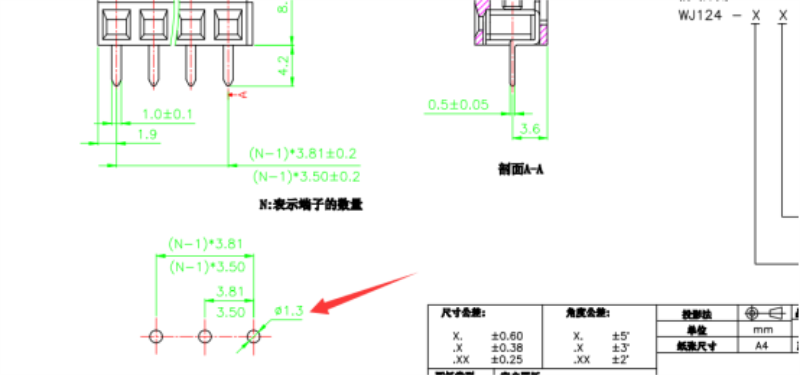

নিচের চিত্রটি দেখুন, WJ124-3.81-4P_WJ124-3.81-4P (KANGNEX) ব্যবহার করে ডিভাইসের পিন 1.3 মিমি, PCB প্যাকেজিং হোল 1.6 মিমি, অ্যাপারচার খুব বড়, ওভার ওয়েভ ওয়েল্ডিং স্পেস টাইম ওয়েল্ডিংয়ের জন্য।

চিত্রের সাথে সংযুক্ত, ডিজাইনের প্রয়োজনীয়তা অনুসারে WJ124-3.81-4P_WJ124-3.81-4P (KANGNEX) উপাদানগুলি কিনুন, পিন 1.3 মিমি সঠিক।

পিসিবি প্যাকেজ গর্তটি ডিভাইসের চেয়ে ছোট

প্লাগ-ইন, কিন্তু তামার গর্ত থাকবে না, যদি এটি একক এবং ডাবল প্যানেল হয় তবে এই পদ্ধতিটি ব্যবহার করা যেতে পারে, একক এবং ডাবল প্যানেলগুলি বাইরের বৈদ্যুতিক পরিবাহী, সোল্ডার পরিবাহী হতে পারে; মাল্টিলেয়ার বোর্ডের প্লাগ-ইন গর্তটি ছোট, এবং পিসিবি বোর্ড কেবল তখনই পুনর্নির্মাণ করা যেতে পারে যদি ভিতরের স্তরে বৈদ্যুতিক পরিবাহী থাকে, কারণ রিমিং দ্বারা ভিতরের স্তর পরিবাহী মেরামত করা যায় না।

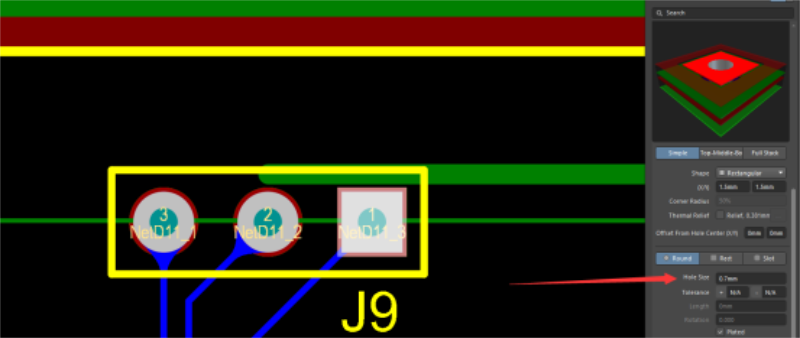

নিচের চিত্রে দেখানো হয়েছে, A2541Hwv-3P_A2541HWV-3P (CJT) এর উপাদানগুলি নকশার প্রয়োজনীয়তা অনুসারে কেনা হয়েছে। পিনটি 1.0 মিমি এবং PCB সিলিং প্যাডের গর্তটি 0.7 মিমি, যার ফলে সন্নিবেশ করা যায়নি।

A2541Hwv-3P_A2541HWV-3P (CJT) এর উপাদানগুলি নকশার প্রয়োজনীয়তা অনুসারে কেনা হয়েছে। পিন 1.0 মিমি সঠিক।

প্যাকেজ পিনের ব্যবধান ডিভাইসের ব্যবধান থেকে আলাদা

ডিআইপি ডিভাইসের পিসিবি সিলিং প্যাডে কেবল পিনের মতোই অ্যাপারচার থাকে না, বরং পিনের গর্তগুলির মধ্যেও একই দূরত্ব প্রয়োজন। যদি পিনের গর্ত এবং ডিভাইসের মধ্যে ব্যবধান অসামঞ্জস্যপূর্ণ হয়, তাহলে ডিভাইসটি ঢোকানো যাবে না, সামঞ্জস্যযোগ্য পায়ের ব্যবধান সহ অংশগুলি ছাড়া।

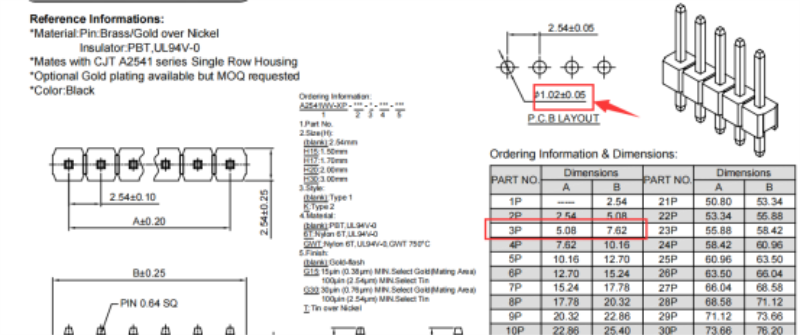

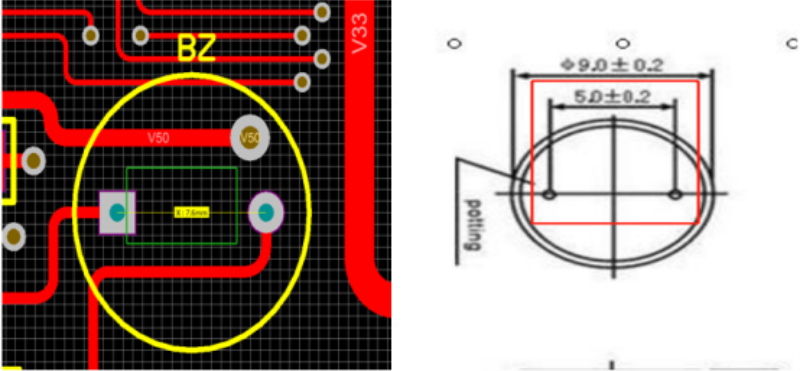

নিচের চিত্রে দেখানো হয়েছে, PCB প্যাকেজিংয়ের পিন হোলের দূরত্ব 7.6 মিমি এবং ক্রয়কৃত উপাদানগুলির পিন হোলের দূরত্ব 5.0 মিমি। 2.6 মিমি পার্থক্যের ফলে ডিভাইসটি ব্যবহারের অযোগ্য হয়ে পড়ে।

পিসিবি প্যাকেজিং গর্তগুলি খুব কাছাকাছি

পিসিবি ডিজাইন, অঙ্কন এবং প্যাকেজিংয়ের ক্ষেত্রে, পিনের গর্তের মধ্যে দূরত্বের দিকে মনোযোগ দেওয়া প্রয়োজন। এমনকি যদি খালি প্লেট তৈরি করা যায়, পিনের গর্তের মধ্যে দূরত্ব কম হয়, তবে ওয়েভ সোল্ডারিংয়ের মাধ্যমে সমাবেশের সময় টিনের শর্ট সার্কিট তৈরি করা সহজ।

নিচের চিত্রে দেখানো হয়েছে, ছোট পিন দূরত্বের কারণে শর্ট সার্কিট হতে পারে। সোল্ডারিং টিনে শর্ট সার্কিটের অনেক কারণ রয়েছে। ডিজাইনের শেষে যদি আগে থেকেই অ্যাসেম্বলিবিলিটি প্রতিরোধ করা যায়, তাহলে সমস্যার প্রকোপ কমানো যেতে পারে।

ডিআইপি ডিভাইস পিন সমস্যা কেস

সমস্যা বর্ণনা

একটি পণ্য ডিআইপি-র ওয়েভ ক্রেস্ট ওয়েল্ডিংয়ের পর, দেখা গেল যে নেটওয়ার্ক সকেটের স্থির পায়ের সোল্ডার প্লেটে টিনের গুরুতর ঘাটতি রয়েছে, যা এয়ার ওয়েল্ডিংয়ের অন্তর্গত।

সমস্যার প্রভাব

ফলস্বরূপ, নেটওয়ার্ক সকেট এবং পিসিবি বোর্ডের স্থায়িত্ব আরও খারাপ হয়ে যায় এবং পণ্য ব্যবহারের সময় সিগন্যাল পিন ফুটের বল প্রয়োগ করা হবে, যা অবশেষে সিগন্যাল পিন ফুটের সংযোগের দিকে পরিচালিত করবে, যা পণ্যের কার্যকারিতাকে প্রভাবিত করবে এবং ব্যবহারকারীদের ব্যবহারে ব্যর্থতার ঝুঁকি তৈরি করবে।

সমস্যা এক্সটেনশন

নেটওয়ার্ক সকেটের স্থিতিশীলতা খারাপ, সিগন্যাল পিনের সংযোগ কর্মক্ষমতা খারাপ, মানসম্মত সমস্যা রয়েছে, তাই এটি ব্যবহারকারীর জন্য নিরাপত্তা ঝুঁকি নিয়ে আসতে পারে, চূড়ান্ত ক্ষতি অকল্পনীয়।

ডিআইপি ডিভাইস সমাবেশ বিশ্লেষণ পরীক্ষা

ডিআইপি ডিভাইস পিন সম্পর্কিত অনেক সমস্যা রয়েছে এবং অনেক মূল বিষয় সহজেই উপেক্ষা করা যায়, যার ফলে চূড়ান্ত স্ক্র্যাপ বোর্ড তৈরি হয়। তাহলে কীভাবে দ্রুত এবং সম্পূর্ণরূপে এই ধরনের সমস্যাগুলি একবারের জন্য সমাধান করা যায়?

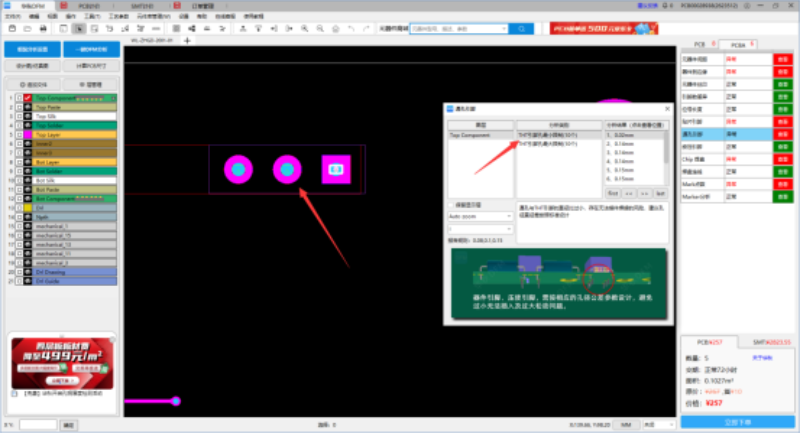

এখানে, আমাদের CHIPSTOCK.TOP সফ্টওয়্যারের অ্যাসেম্বলি এবং বিশ্লেষণ ফাংশনটি DIP ডিভাইসের পিনগুলিতে বিশেষ পরিদর্শন পরিচালনা করতে ব্যবহার করা যেতে পারে। পরিদর্শন আইটেমগুলির মধ্যে রয়েছে গর্তের মধ্য দিয়ে পিনের সংখ্যা, THT পিনের বৃহৎ সীমা, THT পিনের ছোট সীমা এবং THT পিনের বৈশিষ্ট্য। পিনের পরিদর্শন আইটেমগুলি মূলত DIP ডিভাইসের নকশায় সম্ভাব্য সমস্যাগুলি কভার করে।

পিসিবি ডিজাইন সম্পন্ন হওয়ার পর, পিসিবিএ অ্যাসেম্বলি বিশ্লেষণ ফাংশনটি আগে থেকেই ডিজাইনের ত্রুটিগুলি আবিষ্কার করতে, উৎপাদনের আগে ডিজাইনের অসঙ্গতিগুলি সমাধান করতে এবং সমাবেশ প্রক্রিয়ায় ডিজাইনের সমস্যা এড়াতে, উৎপাদন সময় বিলম্বিত করতে এবং গবেষণা ও উন্নয়ন খরচ নষ্ট করতে ব্যবহার করা যেতে পারে।

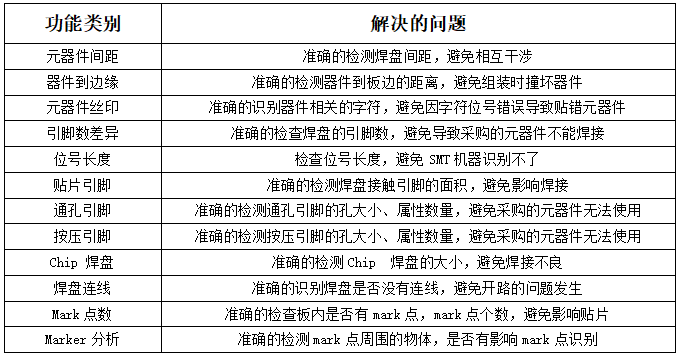

এর অ্যাসেম্বলি বিশ্লেষণ ফাংশনে ১০টি প্রধান আইটেম এবং ২৩৪টি সূক্ষ্ম আইটেম পরিদর্শনের নিয়ম রয়েছে, যা ডিভাইস বিশ্লেষণ, পিন বিশ্লেষণ, প্যাড বিশ্লেষণ ইত্যাদির মতো সম্ভাব্য সমস্ত সমাবেশ সমস্যা কভার করে, যা বিভিন্ন ধরণের উৎপাদন পরিস্থিতি সমাধান করতে পারে যা ইঞ্জিনিয়াররা আগে থেকে অনুমান করতে পারেন না।

পোস্টের সময়: জুলাই-০৫-২০২৩